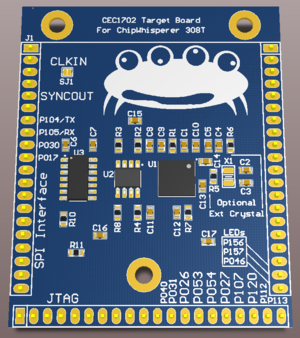

CW308T-CEC1702

| CW308T-CEC1702 | |

|---|---|

| |

| Target Device | MCHP CEC1702 |

| Target Architecture | ARM Cortex M4F |

| Hardware Crypto | AES, SHA, RSA |

| Supported Apps | [] |

| Programmer | Generic SPI Flash Programmer |

| Status | In Development |

I/O Connections

| CW308 Pin | CEC1702 Pin | Function |

|---|---|---|

| GPIO1 | P104 (TXD0) | Serial OUTPUT from CEC1702 |

| GPIO2 | P105 (RXD0) | Serial INPUT to CEC1702 |

| GPIO3 | P030 | GPIO |

| GPIO4 | P017 | Trigger pin |

| CLKIN | XTAL2 | Optional CLKIN |

| CLKFB | P002 (PWM5) | Can output 12MHz PWM on this pin. Useful for synchronizing to internal oscillator |

| J_TRST | JTAG_RST | JTAG Reset |

| J_TDI | JTAG_TDI | JTAG TDI |

| J_TDO | JTAG_TDO | JTAG TDO |

| J_TMS | JTAG_TMS | JTAG TMS |

| J_TCK | JTAG_CLK | JTAG Clock |

| LED1 | P156 | GPIO, Breathing LED0 |

| LED2 | P157 | GPIO, Breathing LED1 |

| LED3 | PA7 | GPIO, LED |

| PDIC | SPI buffer output enable, drive high to enable SPI programming and sniffing | |

| PDID/CS | QSPI0_CS | SPI chip select for SPI flash chip |

| H1 | P040 | GPIO |

| H2 | P031 | GPIO |

| H3 | P026 | GPIO |

| H4 | P053 | GPIO |

| H5 | P054 | GPIO |

| H6 | P027 | GPIO |

| H7 | P107 | GPIO |

| H8 | P120 | GPIO |

| H9 | P112 | GPIO |

| H10 | P113 | GPIO |

Hardware Cryptography

Multi-purpose AES Cryptographic Engine

- Hardware support for ECB, CTR, CBC, and OFB AES modes

- Support for 128-bit, 192-bit and 256-bit key length

- DMA interface to SRAM, shared with Hash engine

Cryptographic Hash Engine

- Support for SHA-1, SHA-256, SHA-512

- DMA interface to SRAM, shared with AES engine

Public Key Cryptographic Engine

- Hardware support for RSA and Elliptic Curve public key algorithms - RSA keys length from 1024 to 4096 bits - ECC Prime Field and Binary Field keys up to 640 bits - Microcoded support for standard public key algorithms

Cryptographic Features

- True Random Number Generator - 1 Kbit FIFO - Monotonic Counter

Programming/Debug Connections

Programming the target involves three